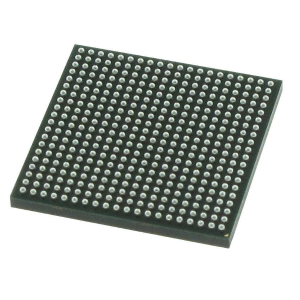

LCMXO1200C-3TN144I FPGA - Filin Ƙofar Ƙofar Tsare-tsare 1200 LUTs 113 IO 1.8 / 2.5/3.3V -3 Spd I

♠ Bayanin samfur

| Siffar Samfur | Siffar Darajar |

| Mai ƙira: | Lattice |

| Rukunin samfur: | FPGA - Filin Tsare-tsaren Ƙofar Ƙofar |

| RoHS: | Cikakkun bayanai |

| Jerin: | Saukewa: LCMXO1200C |

| Adadin Abubuwan Hankali: | 1200 LE |

| Adadin I/Os: | 113 I/O |

| Samar da Wutar Lantarki - Min: | 1.71 V |

| Ƙarfin Ƙarfafawa - Max: | 3.465 V |

| Mafi ƙarancin zafin aiki: | -40 C |

| Matsakaicin Yanayin Aiki: | + 100 C |

| Yawan Bayanai: | - |

| Adadin Masu Canjawa: | - |

| Salon hawa: | SMD/SMT |

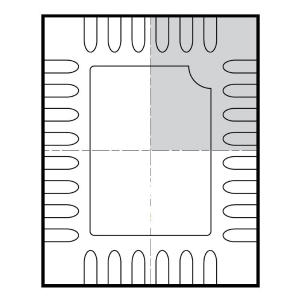

| Kunshin/Kasuwa: | Saukewa: TQFP-144 |

| Marufi: | Tire |

| Alamar: | Lattice |

| RAM da aka rarraba: | 6.4 kbit |

| Toshewar RAM - EBR: | 9.2 kbit |

| Tsayi: | 1.4 mm |

| Tsawon: | 20 mm |

| Matsakaicin Mitar Aiki: | 500 MHz |

| Danshi Mai Hankali: | Ee |

| Adadin Tubalan Ma'auni Array - LABs: | 150 LAB |

| Kayan Aiki Na Yanzu: | 21mA ku |

| Wutar Lantarki Mai Aiki: | 1.8V/2.5V/3.3V |

| Nau'in Samfur: | FPGA - Filin Tsare-tsaren Ƙofar Ƙofar |

| Yawan Kunshin Masana'anta: | 60 |

| Rukuni: | Logic ICs na shirye-shirye |

| Jimlar Ƙwaƙwalwa: | 15.6 kbit |

| Nisa: | 20 mm |

| Nauyin Raka'a: | 1.319 g |

Mara maras tabbas, Mara iyaka Mai sake daidaitawa

• Nan take – yana yin ƙarfi a cikin daƙiƙa guda

Guntu guda ɗaya, babu ƙwaƙwalwar ajiyar waje da ake buƙata

• Kyakkyawan tsaro na ƙira, babu rafi don tsangwama

Sake saita dabaru na tushen SRAM a cikin millise seconds

• SRAM da ƙwaƙwalwar ajiyar da ba ta da ƙarfi wanda za'a iya tsara ta ta tashar JTAG

• Yana goyan bayan shirye-shiryen baya na ƙwaƙwalwar mara mara ƙarfi

Yanayin Barci

• Yana ba da damar ragewa a tsaye har zuwa 100x

Sake saita TransFR™ (TFR)

• Sabunta dabaru na cikin filin yayin da tsarin ke aiki

Babban I/O zuwa Logic Density

• 256 zuwa 2280 LUT4s

73 zuwa 271 I/Os tare da zaɓuɓɓukan fakiti masu yawa

• Goyan bayan ƙaura mai yawa

• Marufi mai yarda da jagorar kyauta/RoHS

Ƙwaƙwalwar ajiya da Rarraba

• Har zuwa 27.6 Kbits sysMEM™ Tushen RAM

• Har zuwa 7.7 Kbits da aka rarraba RAM

• Ƙaddamar da dabarar sarrafa FIFO

I/O Mai Sauƙi

sysIO™ mai shirye-shirye yana goyan bayan kewayon musaya:

- LVCMOS 3.3 / 2.5 / 1.8 / 1.5 / 1.2

- LVTTL

- PCI

- LVDS, Bas-LVDS, LVPECL, RSDS

sysCLOCK™ PLLs

• Har zuwa PLLs analog guda biyu a kowace na'ura

• Girman agogo, rarrabuwa, da jujjuya lokaci

Tallafin Matsayin Tsarin

• IEEE Standard 1149.1 Boundary Scan

• Kan jirgin oscillator

• Na'urori suna aiki da wutar lantarki 3.3V, 2.5V, 1.8V ko 1.2V

• IEEE 1532 mai yarda da shirye-shiryen cikin-tsarin